Difference between revisions of "MuonPi Board"

(Created page with "The MuonPi board is designed as plug-on board for the Raspberry Pi B+ in a form factor conforming with the [https://github.com/raspberrypi/hats RPi HAT specifications]. == Fu...") |

|||

| Line 1: | Line 1: | ||

| − | + | Das MuonPi-Board ist als Aufsteckplatine für den Raspberry Pi B+ in einem Formfaktor konzipiert, der den [https://github.com/raspberrypi/hats RPi HAT Spezifikationen] entspricht. | |

| − | == | + | == Funktionsbeschreibung == |

| − | + | Die MuonPi-Karte implementiert folgende Funktionalitäten: | |

| − | * | + | * Zwei Eingangskanäle |

| − | * | + | * Versorgungsspannung zur Fernspeisung des [[Vorverstärker]]s über die Signalleitung: Die Spannung kann über ein GPIO-Signal ein-/ausgeschaltet werden (individuell für die beiden Kanäle). Sie beinhaltet eine Überstrom- und Übertemperaturabschaltung sowie ein Fehlerrückmeldesignal. |

| − | * Bias | + | * Bias-Spannungsversorgung für den SiPM-Sensor und Bias-Spannungs-/Stromüberwachung. Ein DC/DC-Wandler erzeugt die benötigte Vorspannung in Sperrrichtung aus der 5V-Schiene des RPi. Die Spannung kann über ein GPIO-Signal ein/ausgeschaltet werden. Die aktuelle Bias-Spannung und der Strom werden über den on-board ADC gemessen. Die Spannung kann über den on-board DAC gesteuert werden (nicht in HW Version 2). |

| − | [[File:MuonPi-blockscheme.png|640px|thumb|right|MuonPi | + | [[File:MuonPi-blockscheme.png|640px|thumb|right|MuonPi Funktionsblockschaltbild]] |

| − | * | + | * Signalinverter für die beiden Signaleingänge für den Fall, dass negative Signale an die Karte angelegt werden. |

| − | * | + | * Schwellwert-Diskriminatoren mit einstellbaren Schwellwerten (DAC-Kanäle 1 und 2) im Bereich von 0,5 mV bis 3V. Die Ausgänge der Diskriminatoren sind LVCMOS-Signale mit einer Länge von ~100 ns. |

| − | * | + | * Beide Kanäle sind logisch durch ein UND-Gatter und ein XOR-Gatter verbunden. Auf diese Weise kann sowohl eine Koinzidenz ("beide gleichzeitig") als auch eine Antikoinzidenz ("nur genau eine") innerhalb eines Zeitfensters von 100 ns festgestellt werden. |

| − | * | + | * Die beiden Gattersignale (AND/XOR) werden zeitlich auf 1 us Länge geformt und der GPIO-Schnittstelle des RPi zur Verfügung gestellt. |

| − | * | + | * Die beiden Diskriminatorsignale und die beiden Logikgattersignale werden einem Multiplexer zugeführt. Dessen Ausgang wird dem Zeitstempelungseingang des u-blox GNSS-Empfängers zugeführt. |

| − | * | + | * Der u-blox GNSS-Empfänger NEO-M8N wird verwendet, um die genaue Zeit- und Frequenzreferenz zu erhalten, um eine ausreichende Genauigkeit der Zeitstempelung auf Nanosekunden-Ebene zu gewährleisten. Der Zeitstempel eines Ereignisses (Vorder- und Rückflanke des am Multiplexer-Ausgang anliegenden Signals) wird über die UART-Schnittstelle durch die Nachricht UBX-TIM-TM2 an den RPi übertragen. |

| − | == | + | == Detaillierte Beschreibung == |

| − | + | Das Design der MuonPi-Platine ist offene Hardware. Es ist vollständig in dem freien EDA-Cloud-Tool definiert [https://easyeda.com EasyEDA]. Die [https://easyeda.com/MuonPi/cosmic_shower_detector_v1-52b8a2536bb6468e9f48412a774951d0_copy_copy aktuelle Arbeitsversion des Designs ist HW Ver 3], die im Folgenden näher erläutert wird. | |

| − | + | Die Vorgängerversionen sind als Referenz verfügbar:[https://easyeda.com/hgzaunick/cosmic_shower_detector_v1-52b8a2536bb6468e9f48412a774951d0_copy HW Ver 2] and [https://easyeda.com/hgzaunick/cosmic_shower_detector_v1-52b8a2536bb6468e9f48412a774951d0 HW Ver 1]. | |

| − | === | + | === Eingangsstufe === |

| − | [[File:Input stage v3.1.png|thumb|640px| | + | [[File:Input stage v3.1.png|thumb|640px|Analoge Eingangsstufe (V3.1)]] |

| − | + | Der Signaleingang besteht aus einem mit 50 Ohm abgeschlossenen Signalweg mit gleichzeitiger Bereitstellung der Vorspannung (VPRE1) zur Fernspeisung des Vorverstärkers. Der AC-Anteil wird ausgekoppelt und dem differentiellen Breitbandverstärker U100/U200 (LMH6550) mit einer Spannungsverstärkung von ~3 zugeführt, so dass der Ausgang symmetrisch um eine mittlere Gleichtaktspannung mit einem nicht invertierten und einem invertierten Signal überlagert ist. Der analoge Schalter U102/U202 (SN74LVC1G3157) wählt in Abhängigkeit vom Schaltersteuereingang (POL1) eines der beiden Signale aus und gibt das kapazitiv gekoppelte Signal an einen schnellen Komparator U2 (TLV3502). Die Schwelle THR1 wird vom DAC U402 bereitgestellt (siehe "RPi-Schnittstelle"). | |

| − | === | + | === Digitaler Impulsprozessor === |

| − | + | Die Ausgänge des Komparators U2 werden mit dem monostabilen Tor U300 zu 100 ns breiten Impulsen zeitlich geformt. Diese sind als Diskriminatorausgänge für beide Kanäle angegeben. Sie sind logisch sowohl mit dem UND-Gatter U304 (das eigentlich ein NOR-Gatter ist, bei dem aber die invertierten Eingänge als UND wirken) als auch mit dem XOR-Gatter U303 verbunden. Diese Signale werden auf 1 us Pulslänge geformt und an GPIO-Pins (EVT_XOR und EVT_AND) geliefert. Die Diskriminatorsignale werden von U306 ebenfalls zeitlich auf ca. 100 ms Länge geformt, um die Anzeige-LEDs für ein erkennbares optisches Signal anzusteuern. Mit dem Multiplexer U305 (74AC151) kann eines der an seinen Eingängen angeschlossenen Signale (EVT_AND, EVT_XOR, DISCR1, DISCR2, TIMEPULSE) ausgewählt und dem Ausgang TIME_MEAS zugeführt werden. Das Auswahlwort wird durch den I2C-Expander U404 (PCF9536) geliefert. Der ausgewählte Ausgang wird auf den Interrupt-Pin des u-Blox NEO GNSS-Chips geleitet, wo die steigende Flanke mit Nanosekunden-Auflösung zeitgestempelt und als UBX-Nachricht TIM-TM2 über die UART-Schnittstelle an den Host gesendet wird. Die Diskriminatorsignale, die zeitgeformten Logikgatter und der invertierte Multiplexer-Ausgang sind alle seriell terminiert, um falsche Triggerung oder falsches Timing aufgrund von Reflexionen zu vermeiden, während der nicht-invertierte Multiplexer-Ausgang, der nur den u-Blox-Interrupt-Pin ansteuert, am Ende mit einem Thevenin-Anpassungsnetzwerk terminiert ist (siehe GNSS-Empfänger). | |

| − | [[File:Digital-pulse processor v3.1.png|thumb|640px| | + | [[File:Digital-pulse processor v3.1.png|thumb|640px|Digitaler-Impuls-Prozessor (V3.1)]] |

| − | === GNSS | + | === GNSS-Empfänger === |

| − | + | Der u-Blox NEO M7/M8N Empfängerchip U700 verarbeitet die Zeitinformationen der GNSS-Satelliten (GPS, Galileo, Glonass, BeiDou, QZSS, SBAS) und synchronisiert seinen lokalen TCXO auf dieses Zeitraster. Die GNSS-Antenne wird an die SMA-Buchse X7 angeschlossen. Der u-Blox-Chip liefert über R700/L700 eine Versorgungsspannung für den Vorverstärker der Antenne. Die digitalen Impulse werden in den Interrupt-Pin EXTINT0 eingespeist, um sowohl die steigenden als auch die fallenden Flanken zeitlich zu erfassen. Die Leitung wird durch das Thevenin-Anpassungsnetzwerk R702/R703 abgeschlossen, das durch den Ausgang des Multiplexers U305 mit ausreichend Strom angesteuert wird. Beachten Sie, dass nur der Typ der AC-Familie eine ausreichende Ansteuerungsstärke hat. Ersetzen Sie diese nicht durch andere Logikfamilien. | |

| − | + | Die Kommunikation mit dem Chip erfolgt über die UART-Schnittstelle, die direkt mit den seriellen Leitungen TxD/RxD des RPi verbunden ist. Zusätzlich wird die I2C-Schnittstelle mit dem I2C-Bus des Boards verbunden. Wie sich herausstellte, erfordert die Kommunikation über I2C einen Master, der in der Lage ist, den Takt zu strecken. Dieses Feature ist auf der RPi-Hardware I2C-Schnittstelle derzeit nicht verfügbar, daher wird die u-Blox I2C-Schnittstelle derzeit nicht verwendet. | |

| − | + | Der 1pps-Zeitimpuls wird, zusätzlich zur Verteilung auf einen GPIO-Pin und die Anzeige-LED409, auf eine 2-polige Stiftleiste J700 (TP_OUT) geroutet, wo er für andere Zwecke zur Verfügung steht. Der u-Blox pps-Ausgang kann auf andere Frequenzen programmiert werden, die z. B. zur PLL-Synchronisation oder zur Disziplinierung eines lokalen Oszillators (GPSDO) verwendet werden können. | |

[[File:Gnss receiver v3.1.png|thumb|640px|GNSS receiver section (V3.1)]] | [[File:Gnss receiver v3.1.png|thumb|640px|GNSS receiver section (V3.1)]] | ||

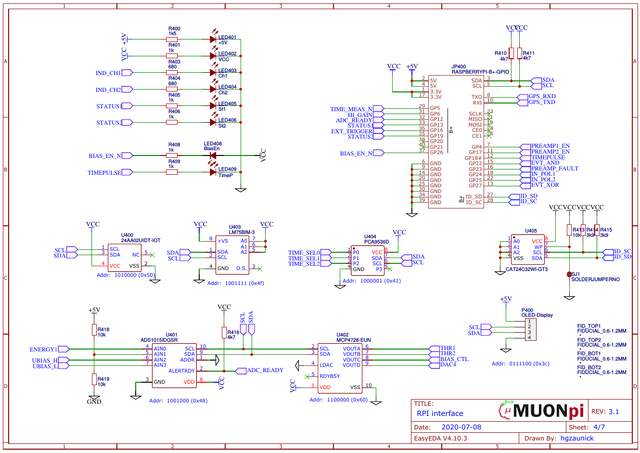

| − | === RPi | + | === RPi-Schnittstelle === |

| − | + | Die Schnittstelle des MuonPi HAT verbindet sich mit dem 40-poligen GPIO-Header des Raspberry-Pi mit mehreren digitalen I/Os, der UART-Schnittstelle vom u-Blox-Chip und der Schnittstelle zum on-board I2C-Bus. Der vierkanalige ADC U401 (ADS1015/1115) erfasst die Spannungen des (optionalen) Peak-Detektors für die Pulsamplitudenmessung (ch1), die On-Board-Versorgungsspannung (nominal 3,3V, durch Spannungsteiler R418/R419 in den Eingangsbereich des ADCs verschoben) auf ch2 und die Sense-Spannungen (nach den Spannungsteilern R505/506 und R507/508) an den beiden Enden des Sense-Widerstands R504 (siehe Abschnitt "Power"), die an den Kanälen 3 bzw. 4 angeschlossen sind. Der 12-Bit-DAC U402 (MCP4728) sorgt für eine feinkörnige Einstellung der beiden Schwellenspannungen (THR1, THR2 an den Kanälen 1 und 2) und der Steuerspannung an Kanal 3 für den DC/DC-Wandler um U502. Kanal 4 wird nicht verwendet, sondern ist auf ein Durchgangsloch-Pad "DAC4" geführt, wo er für beliebige Zwecke verwendet werden kann. Auf der Platine befinden sich zwei I2C-EEPROM-Chips. U400 (24AA02UID) ist für die MuonPi-spezifische Speicherung von Kalibrierungsparametern und der werksseitig programmierten eindeutigen ID, während U405 (CAT24C32WI), der eigentlich an die für genau diesen Zweck vorgesehene RPi-ID-I2C-Schnittstelle angeschlossen ist, die Konfigurationsparameter für die HAT-Identifikation und die automatische GPIO- und Boot-Overlay-Auswahl während der Boot-Phase liefert. | |

| − | + | Darüber hinaus werden auch der Temperatursensor U403 (LM75A/B) und der 4-Bit-I/O-Expander U404 über den on-board I2C-Bus angesteuert. Der I/O-Expander-Chip U404 liefert das Auswahl-Bitmuster für den Multiplexer U305. | |

| − | [[File:Rpi interface v3.1.png|thumb|640px|RPi | + | [[File:Rpi interface v3.1.png|thumb|640px|RPi-Schnittstellenteil mit ADC, DAC, EEPROM, Temperatursensor, OLED-Schnittstelle und LEDs. (V3.1)]] |

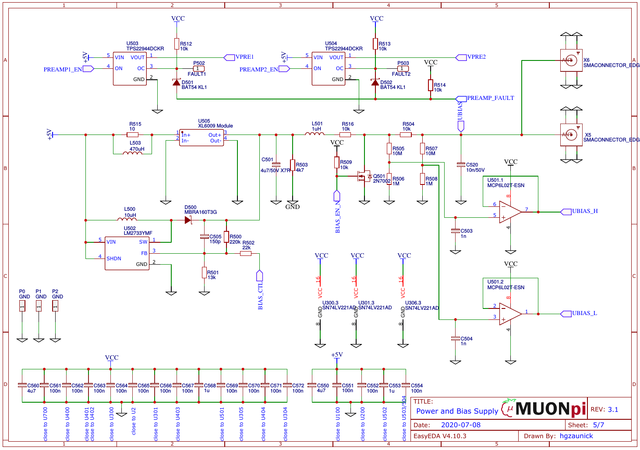

| − | === | + | === Stromversorgung/Bias-Versorgung === |

| − | + | Die Bias-Spannungserzeugung für den SiPM-Fotodetektor ist auf zwei Arten vorgesehen, die jeweils in Abhängigkeit von der Montage ausgewählt werden. Standardmäßig wird die Vorspannung von <33V durch den DC/DC-Wandler um U502 (LM2733Y) erzeugt. Seine Ausgangsspannung wird durch die von Kanal 3 des DAC (U402) gelieferte Spannung gesteuert, wobei der Schnittpunkt durch das ohmsche Teilernetzwerk R500 zu R502 eingestellt wird. Der gefilterte Ausgang wird durch R503 auf Masse geshuntet, um eine schwankende Belastung der Wandlerschaltung zu vermeiden. Nach der HF-Filterung durch L501 wird die Spannung durch den strombegrenzenden Serienwiderstand R516 geleitet und durch den n-Mosfet Q501 überbrückt, der die Spannung gegen Masse kurzschließt, wenn das Steuersignal BIAS_EN_N niedrig ist. Andernfalls wird die Ausgangsspannung, die nicht Null ist, durch den Strommess-Shunt R504 geleitet. Die symmetrischen Widerstandsteiler R505/R506 und R507/R508 zapfen die Spannungen auf beiden Seiten von R504 an, die durch C503/C504 tiefpassgefiltert und von U501 gepuffert werden, bevor sie an die ADC-Kanäle 3 und 4 weitergeleitet werden. Diese Schaltung realisiert sowohl die Messung der aktuellen Bias-Spannung an den Ausgängen X5,X6 als auch die Messung des Bias-Stroms. | |

| − | + | Alternativ kann die Bias-Versorgung auch durch ein externes, aufsteckbares Modul U505 erfolgen. Dies kann sinnvoll sein, wenn Photodetektoren mit anderen Bias-Spannungs-Spezifikationen verwendet werden, z.B. SiPMs vom Typ Hamamatsu mit größeren Betriebsspannungen von ~50..90V. Wenn die Bias-Spannung von einem solchen externen DC/DC-Wandler geliefert wird, ist darauf zu achten, dass der On-Board-Wandler U502 und die zugehörigen Komponenten nicht montiert werden. | |

| − | + | Die Versorgungsspannung von +5V für die Vorverstärker wird über die strombegrenzten Lastschalter U503/U504 (TPS22944) gesteuert. Die Schalter werden unabhängig voneinander mit einem High-Pegel an PREAMP1/2_EN-Signalen vom GPIO freigegeben. Die Fehlerausgänge der Schalter sind mit D501/D502 diode-OR-verknüpft und liefern einen Fehlereingang an den MuonPi in einem der folgenden Fälle: Überstrom (>100mA) und Übertemperatur. In allen Fällen schaltet der Schalter den Ausgang ab, bis die Fehlerbedingung beseitigt ist. | |

| − | [[File:Power section v3.1.png|thumb|640px|Power | + | [[File:Power section v3.1.png|thumb|640px|Power-Management und Bias-Spannungserzeugung (V3.1)]] |

Latest revision as of 22:28, 5 January 2021

Das MuonPi-Board ist als Aufsteckplatine für den Raspberry Pi B+ in einem Formfaktor konzipiert, der den RPi HAT Spezifikationen entspricht.

Contents

Funktionsbeschreibung

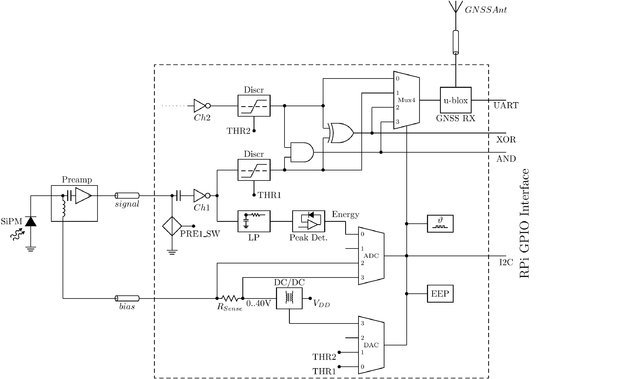

Die MuonPi-Karte implementiert folgende Funktionalitäten:

- Zwei Eingangskanäle

- Versorgungsspannung zur Fernspeisung des Vorverstärkers über die Signalleitung: Die Spannung kann über ein GPIO-Signal ein-/ausgeschaltet werden (individuell für die beiden Kanäle). Sie beinhaltet eine Überstrom- und Übertemperaturabschaltung sowie ein Fehlerrückmeldesignal.

- Bias-Spannungsversorgung für den SiPM-Sensor und Bias-Spannungs-/Stromüberwachung. Ein DC/DC-Wandler erzeugt die benötigte Vorspannung in Sperrrichtung aus der 5V-Schiene des RPi. Die Spannung kann über ein GPIO-Signal ein/ausgeschaltet werden. Die aktuelle Bias-Spannung und der Strom werden über den on-board ADC gemessen. Die Spannung kann über den on-board DAC gesteuert werden (nicht in HW Version 2).

- Signalinverter für die beiden Signaleingänge für den Fall, dass negative Signale an die Karte angelegt werden.

- Schwellwert-Diskriminatoren mit einstellbaren Schwellwerten (DAC-Kanäle 1 und 2) im Bereich von 0,5 mV bis 3V. Die Ausgänge der Diskriminatoren sind LVCMOS-Signale mit einer Länge von ~100 ns.

- Beide Kanäle sind logisch durch ein UND-Gatter und ein XOR-Gatter verbunden. Auf diese Weise kann sowohl eine Koinzidenz ("beide gleichzeitig") als auch eine Antikoinzidenz ("nur genau eine") innerhalb eines Zeitfensters von 100 ns festgestellt werden.

- Die beiden Gattersignale (AND/XOR) werden zeitlich auf 1 us Länge geformt und der GPIO-Schnittstelle des RPi zur Verfügung gestellt.

- Die beiden Diskriminatorsignale und die beiden Logikgattersignale werden einem Multiplexer zugeführt. Dessen Ausgang wird dem Zeitstempelungseingang des u-blox GNSS-Empfängers zugeführt.

- Der u-blox GNSS-Empfänger NEO-M8N wird verwendet, um die genaue Zeit- und Frequenzreferenz zu erhalten, um eine ausreichende Genauigkeit der Zeitstempelung auf Nanosekunden-Ebene zu gewährleisten. Der Zeitstempel eines Ereignisses (Vorder- und Rückflanke des am Multiplexer-Ausgang anliegenden Signals) wird über die UART-Schnittstelle durch die Nachricht UBX-TIM-TM2 an den RPi übertragen.

Detaillierte Beschreibung

Das Design der MuonPi-Platine ist offene Hardware. Es ist vollständig in dem freien EDA-Cloud-Tool definiert EasyEDA. Die aktuelle Arbeitsversion des Designs ist HW Ver 3, die im Folgenden näher erläutert wird.

Die Vorgängerversionen sind als Referenz verfügbar:HW Ver 2 and HW Ver 1.

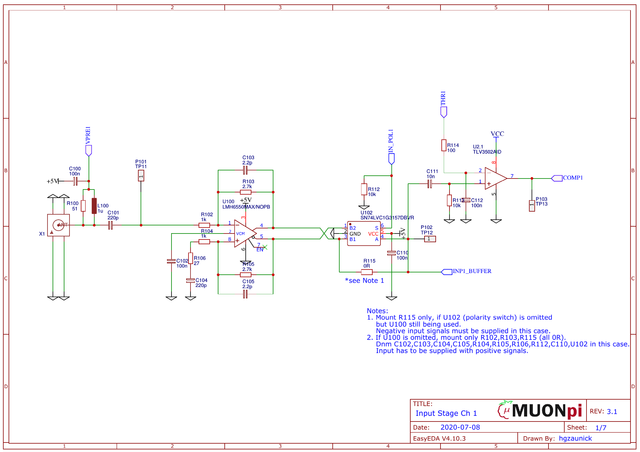

Eingangsstufe

Der Signaleingang besteht aus einem mit 50 Ohm abgeschlossenen Signalweg mit gleichzeitiger Bereitstellung der Vorspannung (VPRE1) zur Fernspeisung des Vorverstärkers. Der AC-Anteil wird ausgekoppelt und dem differentiellen Breitbandverstärker U100/U200 (LMH6550) mit einer Spannungsverstärkung von ~3 zugeführt, so dass der Ausgang symmetrisch um eine mittlere Gleichtaktspannung mit einem nicht invertierten und einem invertierten Signal überlagert ist. Der analoge Schalter U102/U202 (SN74LVC1G3157) wählt in Abhängigkeit vom Schaltersteuereingang (POL1) eines der beiden Signale aus und gibt das kapazitiv gekoppelte Signal an einen schnellen Komparator U2 (TLV3502). Die Schwelle THR1 wird vom DAC U402 bereitgestellt (siehe "RPi-Schnittstelle").

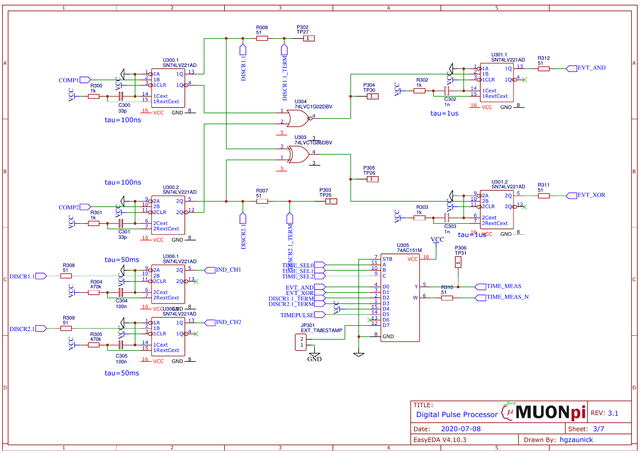

Digitaler Impulsprozessor

Die Ausgänge des Komparators U2 werden mit dem monostabilen Tor U300 zu 100 ns breiten Impulsen zeitlich geformt. Diese sind als Diskriminatorausgänge für beide Kanäle angegeben. Sie sind logisch sowohl mit dem UND-Gatter U304 (das eigentlich ein NOR-Gatter ist, bei dem aber die invertierten Eingänge als UND wirken) als auch mit dem XOR-Gatter U303 verbunden. Diese Signale werden auf 1 us Pulslänge geformt und an GPIO-Pins (EVT_XOR und EVT_AND) geliefert. Die Diskriminatorsignale werden von U306 ebenfalls zeitlich auf ca. 100 ms Länge geformt, um die Anzeige-LEDs für ein erkennbares optisches Signal anzusteuern. Mit dem Multiplexer U305 (74AC151) kann eines der an seinen Eingängen angeschlossenen Signale (EVT_AND, EVT_XOR, DISCR1, DISCR2, TIMEPULSE) ausgewählt und dem Ausgang TIME_MEAS zugeführt werden. Das Auswahlwort wird durch den I2C-Expander U404 (PCF9536) geliefert. Der ausgewählte Ausgang wird auf den Interrupt-Pin des u-Blox NEO GNSS-Chips geleitet, wo die steigende Flanke mit Nanosekunden-Auflösung zeitgestempelt und als UBX-Nachricht TIM-TM2 über die UART-Schnittstelle an den Host gesendet wird. Die Diskriminatorsignale, die zeitgeformten Logikgatter und der invertierte Multiplexer-Ausgang sind alle seriell terminiert, um falsche Triggerung oder falsches Timing aufgrund von Reflexionen zu vermeiden, während der nicht-invertierte Multiplexer-Ausgang, der nur den u-Blox-Interrupt-Pin ansteuert, am Ende mit einem Thevenin-Anpassungsnetzwerk terminiert ist (siehe GNSS-Empfänger).

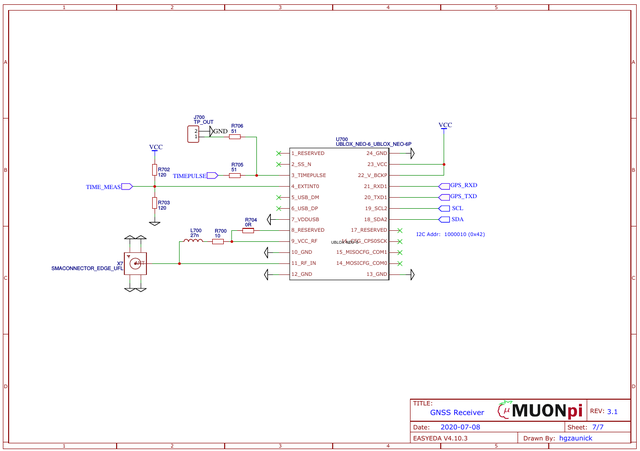

GNSS-Empfänger

Der u-Blox NEO M7/M8N Empfängerchip U700 verarbeitet die Zeitinformationen der GNSS-Satelliten (GPS, Galileo, Glonass, BeiDou, QZSS, SBAS) und synchronisiert seinen lokalen TCXO auf dieses Zeitraster. Die GNSS-Antenne wird an die SMA-Buchse X7 angeschlossen. Der u-Blox-Chip liefert über R700/L700 eine Versorgungsspannung für den Vorverstärker der Antenne. Die digitalen Impulse werden in den Interrupt-Pin EXTINT0 eingespeist, um sowohl die steigenden als auch die fallenden Flanken zeitlich zu erfassen. Die Leitung wird durch das Thevenin-Anpassungsnetzwerk R702/R703 abgeschlossen, das durch den Ausgang des Multiplexers U305 mit ausreichend Strom angesteuert wird. Beachten Sie, dass nur der Typ der AC-Familie eine ausreichende Ansteuerungsstärke hat. Ersetzen Sie diese nicht durch andere Logikfamilien. Die Kommunikation mit dem Chip erfolgt über die UART-Schnittstelle, die direkt mit den seriellen Leitungen TxD/RxD des RPi verbunden ist. Zusätzlich wird die I2C-Schnittstelle mit dem I2C-Bus des Boards verbunden. Wie sich herausstellte, erfordert die Kommunikation über I2C einen Master, der in der Lage ist, den Takt zu strecken. Dieses Feature ist auf der RPi-Hardware I2C-Schnittstelle derzeit nicht verfügbar, daher wird die u-Blox I2C-Schnittstelle derzeit nicht verwendet. Der 1pps-Zeitimpuls wird, zusätzlich zur Verteilung auf einen GPIO-Pin und die Anzeige-LED409, auf eine 2-polige Stiftleiste J700 (TP_OUT) geroutet, wo er für andere Zwecke zur Verfügung steht. Der u-Blox pps-Ausgang kann auf andere Frequenzen programmiert werden, die z. B. zur PLL-Synchronisation oder zur Disziplinierung eines lokalen Oszillators (GPSDO) verwendet werden können.

RPi-Schnittstelle

Die Schnittstelle des MuonPi HAT verbindet sich mit dem 40-poligen GPIO-Header des Raspberry-Pi mit mehreren digitalen I/Os, der UART-Schnittstelle vom u-Blox-Chip und der Schnittstelle zum on-board I2C-Bus. Der vierkanalige ADC U401 (ADS1015/1115) erfasst die Spannungen des (optionalen) Peak-Detektors für die Pulsamplitudenmessung (ch1), die On-Board-Versorgungsspannung (nominal 3,3V, durch Spannungsteiler R418/R419 in den Eingangsbereich des ADCs verschoben) auf ch2 und die Sense-Spannungen (nach den Spannungsteilern R505/506 und R507/508) an den beiden Enden des Sense-Widerstands R504 (siehe Abschnitt "Power"), die an den Kanälen 3 bzw. 4 angeschlossen sind. Der 12-Bit-DAC U402 (MCP4728) sorgt für eine feinkörnige Einstellung der beiden Schwellenspannungen (THR1, THR2 an den Kanälen 1 und 2) und der Steuerspannung an Kanal 3 für den DC/DC-Wandler um U502. Kanal 4 wird nicht verwendet, sondern ist auf ein Durchgangsloch-Pad "DAC4" geführt, wo er für beliebige Zwecke verwendet werden kann. Auf der Platine befinden sich zwei I2C-EEPROM-Chips. U400 (24AA02UID) ist für die MuonPi-spezifische Speicherung von Kalibrierungsparametern und der werksseitig programmierten eindeutigen ID, während U405 (CAT24C32WI), der eigentlich an die für genau diesen Zweck vorgesehene RPi-ID-I2C-Schnittstelle angeschlossen ist, die Konfigurationsparameter für die HAT-Identifikation und die automatische GPIO- und Boot-Overlay-Auswahl während der Boot-Phase liefert. Darüber hinaus werden auch der Temperatursensor U403 (LM75A/B) und der 4-Bit-I/O-Expander U404 über den on-board I2C-Bus angesteuert. Der I/O-Expander-Chip U404 liefert das Auswahl-Bitmuster für den Multiplexer U305.

Stromversorgung/Bias-Versorgung

Die Bias-Spannungserzeugung für den SiPM-Fotodetektor ist auf zwei Arten vorgesehen, die jeweils in Abhängigkeit von der Montage ausgewählt werden. Standardmäßig wird die Vorspannung von <33V durch den DC/DC-Wandler um U502 (LM2733Y) erzeugt. Seine Ausgangsspannung wird durch die von Kanal 3 des DAC (U402) gelieferte Spannung gesteuert, wobei der Schnittpunkt durch das ohmsche Teilernetzwerk R500 zu R502 eingestellt wird. Der gefilterte Ausgang wird durch R503 auf Masse geshuntet, um eine schwankende Belastung der Wandlerschaltung zu vermeiden. Nach der HF-Filterung durch L501 wird die Spannung durch den strombegrenzenden Serienwiderstand R516 geleitet und durch den n-Mosfet Q501 überbrückt, der die Spannung gegen Masse kurzschließt, wenn das Steuersignal BIAS_EN_N niedrig ist. Andernfalls wird die Ausgangsspannung, die nicht Null ist, durch den Strommess-Shunt R504 geleitet. Die symmetrischen Widerstandsteiler R505/R506 und R507/R508 zapfen die Spannungen auf beiden Seiten von R504 an, die durch C503/C504 tiefpassgefiltert und von U501 gepuffert werden, bevor sie an die ADC-Kanäle 3 und 4 weitergeleitet werden. Diese Schaltung realisiert sowohl die Messung der aktuellen Bias-Spannung an den Ausgängen X5,X6 als auch die Messung des Bias-Stroms.

Alternativ kann die Bias-Versorgung auch durch ein externes, aufsteckbares Modul U505 erfolgen. Dies kann sinnvoll sein, wenn Photodetektoren mit anderen Bias-Spannungs-Spezifikationen verwendet werden, z.B. SiPMs vom Typ Hamamatsu mit größeren Betriebsspannungen von ~50..90V. Wenn die Bias-Spannung von einem solchen externen DC/DC-Wandler geliefert wird, ist darauf zu achten, dass der On-Board-Wandler U502 und die zugehörigen Komponenten nicht montiert werden.

Die Versorgungsspannung von +5V für die Vorverstärker wird über die strombegrenzten Lastschalter U503/U504 (TPS22944) gesteuert. Die Schalter werden unabhängig voneinander mit einem High-Pegel an PREAMP1/2_EN-Signalen vom GPIO freigegeben. Die Fehlerausgänge der Schalter sind mit D501/D502 diode-OR-verknüpft und liefern einen Fehlereingang an den MuonPi in einem der folgenden Fälle: Überstrom (>100mA) und Übertemperatur. In allen Fällen schaltet der Schalter den Ausgang ab, bis die Fehlerbedingung beseitigt ist.